- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

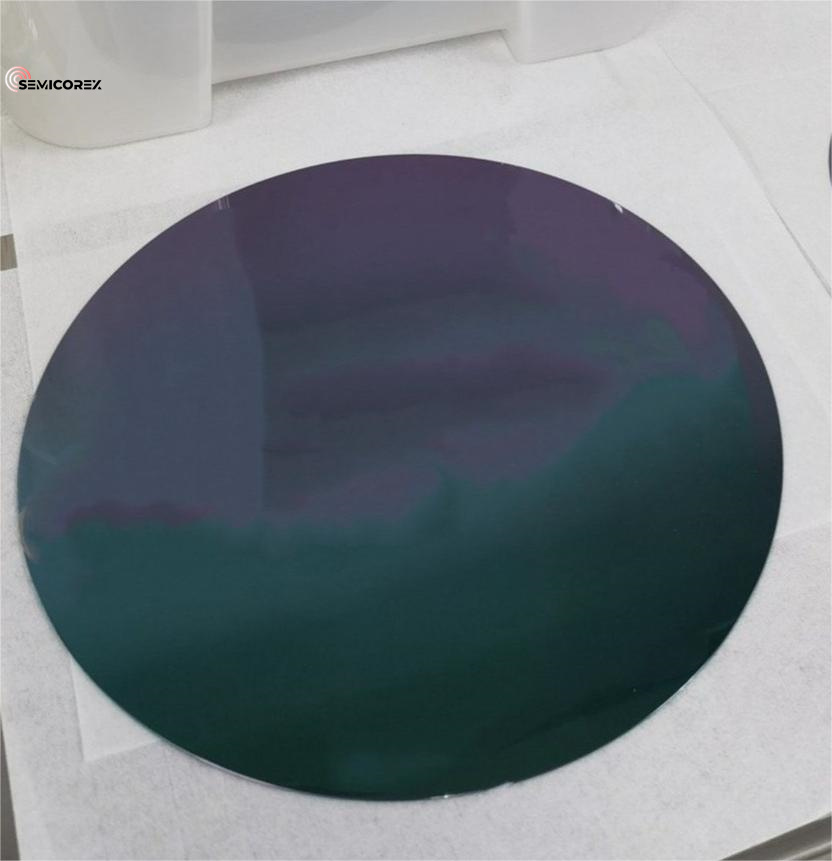

Silicon Wafer

ວັດສະດຸ Silicon ເປັນວັດສະດຸແຂງທີ່ມີຄຸນສົມບັດໄຟຟ້າ semiconductor ທີ່ແນ່ນອນແລະຄວາມຫມັ້ນຄົງທາງດ້ານຮ່າງກາຍ, ແລະສະຫນອງການສະຫນັບສະຫນູນ substrate ສໍາລັບຂະບວນການຜະລິດວົງຈອນປະສົມປະສານຕໍ່ມາ. ມັນເປັນວັດສະດຸທີ່ສໍາຄັນສໍາລັບວົງຈອນປະສົມປະສານທີ່ໃຊ້ຊິລິໂຄນ. ຫຼາຍກວ່າ 95% ຂອງອຸປະກອນ semiconductor ແລະຫຼາຍກວ່າ 90% ຂອງວົງຈອນປະສົມປະສານໃນໂລກແມ່ນເຮັດຢູ່ໃນ wafers ຊິລິໂຄນ.

ອີງຕາມວິທີການຂະຫຍາຍຕົວໄປເຊຍກັນດຽວທີ່ແຕກຕ່າງກັນ, ຊິລິໂຄນໄປເຊຍກັນດຽວແບ່ງອອກເປັນສອງປະເພດ: Czochralski (CZ) ແລະເຂດເລື່ອນ (FZ). wafers Silicon ສາມາດແບ່ງອອກເປັນສາມປະເພດ: wafers ຂັດ, wafers epitaxial, ແລະ Silicon-On-insulator (SOI).

wafer ຂັດຊິລິໂຄນ ຫມາຍເຖິງ aຊິລິຄອນ waferສ້າງຕັ້ງຂຶ້ນໂດຍການຂັດພື້ນຜິວ. ມັນເປັນ wafer ຮອບທີ່ມີຄວາມຫນາຫນ້ອຍກວ່າ 1mm ປຸງແຕ່ງໂດຍການຕັດ, ຂັດ, ຂັດ, ທໍາຄວາມສະອາດແລະຂະບວນການອື່ນໆຂອງ rod ໄປເຊຍກັນດຽວ. ມັນຖືກນໍາໃຊ້ຕົ້ນຕໍໃນວົງຈອນປະສົມປະສານແລະອຸປະກອນແຍກແລະຄອບຄອງຕໍາແຫນ່ງທີ່ສໍາຄັນໃນລະບົບຕ່ອງໂສ້ອຸດສາຫະກໍາ semiconductor.

ເມື່ອອົງປະກອບກຸ່ມ V ເຊັ່ນ phosphorus, antimony, arsenic, ແລະອື່ນໆຖືກ doped ເຂົ້າໄປໃນຊິລິໂຄນໄປເຊຍກັນດຽວ, N-type conductive material ຈະຖືກສ້າງຕັ້ງຂຶ້ນ; ເມື່ອອົງປະກອບຂອງກຸ່ມ III ເຊັ່ນ boron ຖືກ doped ເຂົ້າໄປໃນຊິລິຄອນ, P-type conductive material ຈະຖືກສ້າງຕັ້ງຂຶ້ນ. ຄວາມຕ້ານທານຂອງຊິລິໂຄນໄປເຊຍກັນດຽວແມ່ນຖືກກໍານົດໂດຍຈໍານວນຂອງອົງປະກອບ doping doped. ປະລິມານ doping ຫຼາຍ, ຄວາມຕ້ານທານຕ່ໍາ. wafers ຂັດ silicon doped ອ່ອນໆໂດຍທົ່ວໄປຫມາຍເຖິງ wafers ຂັດຊິລິໂຄນທີ່ມີຄວາມຕ້ານທານຫຼາຍກ່ວາ 0.1W·cm, ເຊິ່ງຖືກນໍາໃຊ້ຢ່າງກວ້າງຂວາງໃນການຜະລິດຂອງວົງຈອນປະສົມປະສານຂະຫນາດໃຫຍ່ແລະຫນ່ວຍຄວາມຈໍາ; wafers ຂັດ silicon doped ຫຼາຍໂດຍທົ່ວໄປແລ້ວຫມາຍເຖິງ wafers ຂັດຊິລິໂຄນທີ່ມີຄວາມຕ້ານທານຫນ້ອຍກວ່າ 0.1W·cm, ເຊິ່ງໂດຍທົ່ວໄປແລ້ວຖືກນໍາໃຊ້ເປັນວັດສະດຸຍ່ອຍສໍາລັບ wafers ຊິລິຄອນ epitaxial ແລະຖືກນໍາໃຊ້ຢ່າງກວ້າງຂວາງໃນການຜະລິດອຸປະກອນໄຟຟ້າ semiconductor.

wafers ຂັດຊິລິໂຄນທີ່ປະກອບເປັນພື້ນທີ່ສະອາດຢູ່ດ້ານຂອງwafers ຊິລິໂຄນຫຼັງຈາກ annealing ຄວາມຮ້ອນແມ່ນເອີ້ນວ່າ wafers silicon annealing. ທີ່ໃຊ້ທົ່ວໄປແມ່ນ wafers ຟອກ hydrogen ແລະ wafers argon annealing. wafers ຊິລິໂຄນ 300mm ແລະບາງ wafers ຊິລິໂຄນ 200mm ທີ່ມີຄວາມຕ້ອງການທີ່ສູງຂຶ້ນຮຽກຮ້ອງໃຫ້ມີການນໍາໃຊ້ຂະບວນການຂັດສອງດ້ານ. ດັ່ງນັ້ນ, ເທກໂນໂລຍີ gettering ພາຍນອກທີ່ແນະນໍາສູນ gettering ຜ່ານທາງຫລັງຂອງ silicon wafer ແມ່ນມີຄວາມຫຍຸ້ງຍາກທີ່ຈະນໍາໃຊ້. ຂະບວນການຮັບພາຍໃນທີ່ນໍາໃຊ້ຂະບວນການ annealing ເພື່ອສ້າງເປັນສູນຮັບພາຍໃນໄດ້ກາຍເປັນຂະບວນການຮັບຕົ້ນຕໍສໍາລັບການ wafers ຊິລິຄອນຂະຫນາດໃຫຍ່. ເມື່ອປຽບທຽບກັບ wafers ຂັດທົ່ວໄປ, wafers annealed ສາມາດປັບປຸງການປະຕິບັດອຸປະກອນແລະເພີ່ມຜົນຜະລິດ, ແລະຖືກນໍາໃຊ້ຢ່າງກວ້າງຂວາງໃນການຜະລິດຂອງວົງຈອນປະສົມປະສານດິຈິຕອນແລະອະນາລັອກແລະຊິບຫນ່ວຍຄວາມຈໍາ.

ຫຼັກການພື້ນຖານຂອງການລະລາຍເຂດການຈະເລີນເຕີບໂຕຂອງໄປເຊຍກັນດຽວແມ່ນອີງໃສ່ຄວາມກົດດັນດ້ານການລະລາຍເພື່ອໂຈະເຂດ molten ລະຫວ່າງ rod ຊິລິຄອນ polycrystalline ແລະໄປເຊຍກັນດຽວທີ່ປູກຢູ່ຂ້າງລຸ່ມນີ້, ແລະຊໍາລະແລະການຂະຫຍາຍຕົວໄປເຊຍກັນຊິລິຄອນດຽວໂດຍການຍ້າຍເຂດ molten ຂຶ້ນ. ໂຊນລະລາຍຊິລິຄອນໄປເຊຍກັນດຽວບໍ່ໄດ້ປົນເປື້ອນໂດຍ crucibles ແລະມີຄວາມບໍລິສຸດສູງ. ພວກເຂົາເຈົ້າແມ່ນເຫມາະສົມສໍາລັບການຜະລິດຂອງ N-type silicon ໄປເຊຍກັນດຽວ (ລວມທັງ neutron transmutation doped ໄປເຊຍກັນດຽວ) ທີ່ມີຄວາມຕ້ານທານສູງກວ່າ 200Ω·cm ແລະຄວາມຕ້ານທານສູງ P-type silicon ໄປເຊຍກັນ. ການລະລາຍເຂດຊິລິໂຄນໄປເຊຍກັນດຽວຖືກນໍາໃຊ້ຕົ້ນຕໍໃນການຜະລິດອຸປະກອນແຮງດັນສູງແລະພະລັງງານສູງ.

Silicon epitaxial waferໝາຍເຖິງວັດສະດຸທີ່ໜຶ່ງ ຫຼືຫຼາຍຊັ້ນຂອງຊິລິໂຄນໜຶ່ງ ຫຼືຫຼາຍຊັ້ນຂອງແຜ່ນບາງໆໄປເຊຍກັນແມ່ນໄດ້ເຕີບໃຫຍ່ຂຶ້ນໂດຍການລະລາຍຂອງໄອພີຕາຊີລເທິງຊັ້ນຍ່ອຍ, ແລະສ່ວນຫຼາຍແມ່ນໃຊ້ໃນການຜະລິດວົງຈອນລວມຕ່າງໆ ແລະອຸປະກອນແຍກກັນ.

ໃນຂະບວນການວົງຈອນປະສົມປະສານ CMOS ຂັ້ນສູງ, ເພື່ອປັບປຸງຄວາມສົມບູນຂອງຊັ້ນອອກໄຊຂອງປະຕູຮົ້ວ, ປັບປຸງການຮົ່ວໄຫຼໃນຊ່ອງທາງ, ແລະເພີ່ມຄວາມຫນ້າເຊື່ອຖືຂອງວົງຈອນປະສົມປະສານ, ແຜ່ນ silicon epitaxial wafers ມັກຈະຖືກນໍາໃຊ້, ນັ້ນແມ່ນ, ຊັ້ນຂອງແຜ່ນ silicon ບາງໆແມ່ນ. epitaxial homogeneously ປູກຢູ່ໃນ wafer ຂັດ silicon doped lightly, ຊຶ່ງສາມາດຫຼີກເວັ້ນການຂໍ້ບົກຜ່ອງຂອງເນື້ອໃນອົກຊີເຈນທີ່ສູງແລະຂໍ້ບົກພ່ອງຈໍານວນຫຼາຍກ່ຽວກັບຫນ້າດິນຂອງ wafers silicon ທົ່ວໄປ; ໃນຂະນະທີ່ສໍາລັບ wafers ຊິລິໂຄນ epitaxial ທີ່ໃຊ້ສໍາລັບວົງຈອນປະສົມປະສານພະລັງງານແລະອຸປະກອນແຍກ, ຊັ້ນຂອງຊັ້ນ epitaxial ຄວາມຕ້ານທານສູງແມ່ນປົກກະຕິແລ້ວ epitaxial ປູກຢູ່ໃນ substrate ຊິລິຄອນຕ້ານທານຕ່ໍາ (wafer silicon ຂັດຫຼາຍ doped ຫຼາຍ). ໃນສະພາບແວດລ້ອມຄໍາຮ້ອງສະຫມັກພະລັງງານສູງແລະແຮງດັນສູງ, ຄວາມຕ້ານທານຕ່ໍາຂອງ substrate ຊິລິໂຄນສາມາດຫຼຸດຜ່ອນການຕໍ່ຕ້ານ, ແລະຊັ້ນ epitaxial ຕ້ານທານສູງສາມາດເພີ່ມແຮງດັນການທໍາລາຍຂອງອຸປະກອນ.

SOI (Silicon-On-Insulator)ແມ່ນຊິລິໂຄນຢູ່ໃນຊັ້ນ insulating. ມັນເປັນໂຄງສ້າງ "sandwich" ທີ່ມີຊັ້ນ silicon ເທິງ (Top Silicon), ຊັ້ນກາງ silicon dioxide ຝັງ (BOX) ແລະຊັ້ນຮອງ silicon ສະຫນັບສະຫນູນ (Handle) ຂ້າງລຸ່ມນີ້. ໃນຖານະເປັນວັດສະດຸ substrate ໃຫມ່ສໍາລັບການຜະລິດວົງຈອນປະສົມປະສານ, ປະໂຫຍດຕົ້ນຕໍຂອງ SOI ແມ່ນວ່າມັນສາມາດບັນລຸການ insulation ໄຟຟ້າສູງໂດຍຜ່ານຊັ້ນ oxide, ປະສິດທິພາບການຫຼຸດຜ່ອນຄວາມຈຸຂອງແມ່ກາຝາກແລະການຮົ່ວໄຫລຂອງ wafers ຊິລິໂຄນ, ທີ່ເອື້ອອໍານວຍໃຫ້ແກ່ການຜະລິດຂອງສູງ. ຄວາມໄວ, ພະລັງງານຕ່ໍາ, ການເຊື່ອມໂຍງສູງແລະຄວາມຫນ້າເຊື່ອຖືສູງຂອງວົງຈອນປະສົມປະສານຂະຫນາດໃຫຍ່ທີ່ສຸດ, ແລະຖືກນໍາໃຊ້ຢ່າງກວ້າງຂວາງໃນອຸປະກອນໄຟຟ້າແຮງດັນສູງ, ອຸປະກອນຕົວຕັ້ງຕົວຕີ optical, MEMS ແລະພາກສະຫນາມອື່ນໆ. ໃນປັດຈຸບັນ, ເຕັກໂນໂລຊີການກະກຽມຂອງວັດສະດຸ SOI ສ່ວນໃຫຍ່ແມ່ນປະກອບດ້ວຍເຕັກໂນໂລຊີການຜູກມັດ (BESOI), ເຕັກໂນໂລຊີ stripping ອັດສະລິຍະ (Smart-Cut), ເຕັກໂນໂລຊີການປູກຝັງອົກຊີເຈນທີ່ ion (SIMOX), ເຕັກໂນໂລຊີສີດພັນທະບັດອົກຊີເຈນ (Simbond), ແລະອື່ນໆ ເຕັກໂນໂລຊີຕົ້ນຕໍແມ່ນ smart. ເຕັກໂນໂລຊີການລອກເອົາ.

SOI wafers ຊິລິຄອນສາມາດແບ່ງອອກເປັນແຜ່ນບາງໆ SOI silicon wafers ແລະແຜ່ນຫນາ SOI silicon wafers. ຄວາມຫນາຂອງຊິລິໂຄນເທິງຂອງແຜ່ນບາງໆSOI wafers ຊິລິຄອນແມ່ນຫນ້ອຍກວ່າ 1um. ໃນປັດຈຸບັນ, 95% ຂອງຕະຫຼາດ SOI silicon wafer ຮູບເງົາບາງໆແມ່ນສຸມໃສ່ໃນຂະຫນາດ 200mm ແລະ 300mm, ແລະຜົນບັງຄັບໃຊ້ຂອງຕະຫຼາດຂອງມັນສ່ວນໃຫຍ່ແມ່ນມາຈາກຜະລິດຕະພັນທີ່ມີຄວາມໄວສູງ, ພະລັງງານຕ່ໍາ, ໂດຍສະເພາະໃນຄໍາຮ້ອງສະຫມັກ microprocessor. ສໍາລັບຕົວຢ່າງ, ໃນຂະບວນການກ້າວຫນ້າທາງດ້ານຕ່ໍາກວ່າ 28nm, ຊິລິໂຄນທີ່ຫມົດໄປຢ່າງເຕັມສ່ວນໃນ insulator (FD-SOI) ມີຄວາມໄດ້ປຽບຂອງການປະຕິບັດຢ່າງຈະແຈ້ງຂອງການບໍລິໂພກພະລັງງານຕ່ໍາ, ການປ້ອງກັນລັງສີ, ແລະການຕໍ່ຕ້ານອຸນຫະພູມສູງ. ໃນເວລາດຽວກັນ, ການນໍາໃຊ້ວິທີແກ້ໄຂ SOI ສາມາດຫຼຸດຜ່ອນຂະບວນການຜະລິດຢ່າງຫຼວງຫຼາຍ. ຄວາມຫນາຂອງຊິລິໂຄນດ້ານເທິງຂອງແຜ່ນຫນາ SOI ແຜ່ນ silicon wafers ແມ່ນຫຼາຍກ່ວາ 1um, ແລະຄວາມຫນາຂອງຊັ້ນຝັງແມ່ນ 0.5-4um. ມັນຖືກນໍາໃຊ້ຕົ້ນຕໍໃນອຸປະກອນພະລັງງານແລະຂົງເຂດ MEMS, ໂດຍສະເພາະໃນການຄວບຄຸມອຸດສາຫະກໍາ, ເຄື່ອງເອເລັກໂຕຣນິກລົດຍົນ, ການສື່ສານໄຮ້ສາຍ, ແລະອື່ນໆ, ແລະປົກກະຕິແລ້ວໃຊ້ຜະລິດຕະພັນທີ່ມີເສັ້ນຜ່າສູນກາງ 150mm ແລະ 200mm.