- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

ຂັດສຸດທ້າຍຂອງຫນ້າດິນ wafer ຊິລິໂຄນ

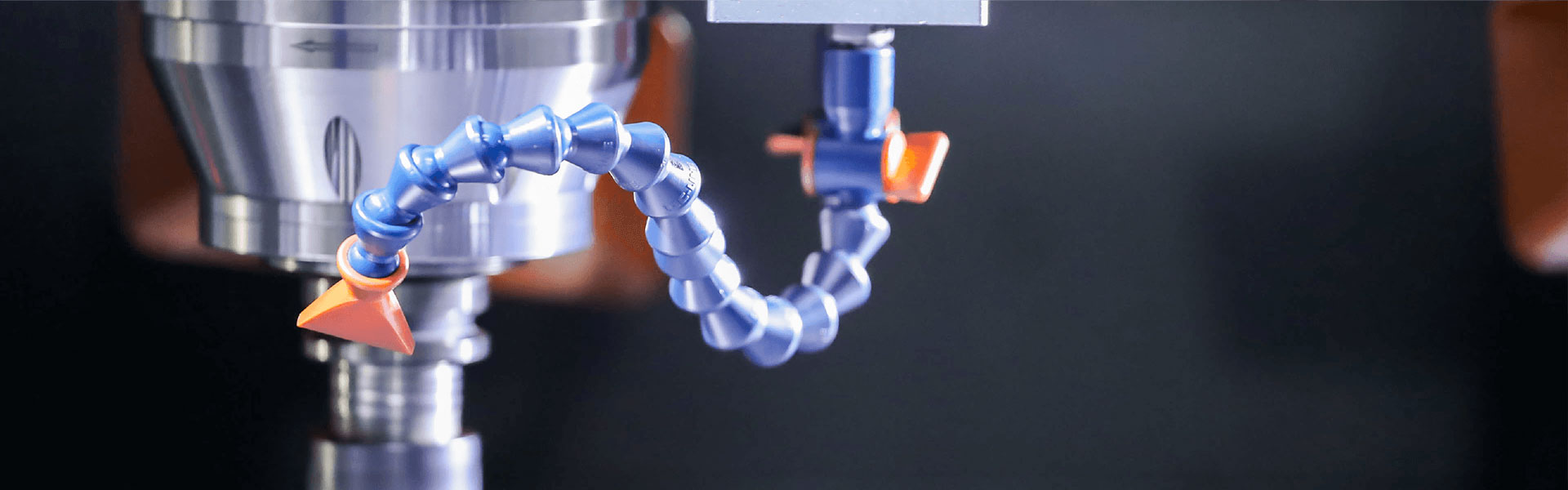

ເພື່ອບັນລຸຄວາມຕ້ອງການທີ່ມີຄຸນນະພາບສູງຂອງຂະບວນການວົງຈອນຊິບ IC ທີ່ມີຄວາມກວ້າງຂອງເສັ້ນຂະຫນາດນ້ອຍກວ່າ 0.13μm ຫາ 28nm ສໍາລັບ wafers ຂັດ silicon ເສັ້ນຜ່າກາງ 300mm, ມັນເປັນສິ່ງຈໍາເປັນເພື່ອຫຼຸດຜ່ອນການປົນເປື້ອນຈາກສິ່ງເສດເຫຼືອ, ເຊັ່ນ: ion ໂລຫະ, ຢູ່ເທິງຫນ້າຂອງ wafer. ນອກຈາກນັ້ນ, ໄດ້ຊິລິຄອນ waferຈະຕ້ອງສະແດງໃຫ້ເຫັນລັກສະນະ nanomorphology ພື້ນຜິວທີ່ສູງທີ່ສຸດ. ດັ່ງນັ້ນ, ການຂັດສຸດທ້າຍ (ຫຼືການຂັດລະອຽດ) ກາຍເປັນຂັ້ນຕອນສໍາຄັນໃນຂະບວນການ.

ການຂັດສຸດທ້າຍນີ້ໂດຍທົ່ວໄປແລ້ວຈະໃຊ້ເທັກໂນໂລຍີການຂັດກົນຈັກທາງເຄມີ (CMP) ທີ່ເປັນດ່າງ colloidal silica. ວິທີການນີ້ລວມເອົາຜົນກະທົບຂອງການກັດກ່ອນທາງເຄມີແລະການຂັດກົນເພື່ອກໍາຈັດຄວາມບໍ່ສົມບູນແລະສິ່ງເສດເຫຼືອຂະຫນາດນ້ອຍຢ່າງມີປະສິດທິພາບແລະຖືກຕ້ອງ.ຊິລິຄອນ waferດ້ານ.

ຢ່າງໃດກໍຕາມ, ໃນຂະນະທີ່ເທກໂນໂລຍີ CMP ແບບດັ້ງເດີມມີປະສິດທິພາບ, ອຸປະກອນສາມາດມີລາຄາແພງ, ແລະການບັນລຸຄວາມແມ່ນຍໍາທີ່ຕ້ອງການສໍາລັບຄວາມກວ້າງຂອງເສັ້ນຂະຫນາດນ້ອຍກວ່າອາດຈະເປັນສິ່ງທ້າທາຍກັບວິທີການຂັດແບບທໍາມະດາ. ດັ່ງນັ້ນ, ອຸດສາຫະກໍາກໍາລັງຂຸດຄົ້ນເຕັກໂນໂລຊີຂັດໃຫມ່, ເຊັ່ນ: ເຕັກໂນໂລຊີ plasma planarization ສານເຄມີແຫ້ງ (D.C.P. plasma technology), ສໍາລັບ wafers ຊິລິຄອນຄວບຄຸມດິຈິຕອນ.

![]()

ເທກໂນໂລຍີ plasma D.C.P ແມ່ນເຕັກໂນໂລຢີການປຸງແຕ່ງທີ່ບໍ່ມີການຕິດຕໍ່. ມັນໃຊ້ SF6 (sulfur hexafluoride) plasma ເພື່ອ etchຊິລິຄອນ waferດ້ານ. ໂດຍການຄວບຄຸມຢ່າງຖືກຕ້ອງ plasma etching ເວລາປຸງແຕ່ງແລະຊິລິຄອນ waferຄວາມໄວການສະແກນແລະຕົວກໍານົດການອື່ນໆ, ມັນສາມາດບັນລຸໄດ້ຄວາມແມ່ນຍໍາສູງ flattening ຂອງຊິລິຄອນ waferດ້ານ. ເມື່ອປຽບທຽບກັບເທກໂນໂລຍີ CMP ແບບດັ້ງເດີມ, ເທກໂນໂລຍີ D.C.P ມີຄວາມຖືກຕ້ອງຂອງການປຸງແຕ່ງທີ່ສູງກວ່າແລະຄວາມຫມັ້ນຄົງ, ແລະສາມາດຫຼຸດຜ່ອນຄ່າໃຊ້ຈ່າຍໃນການດໍາເນີນງານຂອງການຂັດ.

ໃນລະຫວ່າງຂະບວນການປຸງແຕ່ງ D.C.P, ຕ້ອງເອົາໃຈໃສ່ເປັນພິເສດຕໍ່ບັນຫາດ້ານວິຊາການຕໍ່ໄປນີ້:

ການຄວບຄຸມແຫຼ່ງ plasma: ໃຫ້ແນ່ໃຈວ່າພາລາມິເຕີເຊັ່ນ SF6(ການຜະລິດ plasma ແລະຄວາມຫນາແຫນ້ນຂອງການໄຫຼວຽນຂອງຄວາມໄວ, ເສັ້ນຜ່າສູນກາງຈຸດການໄຫຼຂອງຄວາມໄວ (ຈຸດສຸມຂອງການໄຫຼຄວາມໄວ)) ໄດ້ຖືກຄວບຄຸມຢ່າງຖືກຕ້ອງເພື່ອບັນລຸການກັດກ່ອນເປັນເອກະພາບໃນດ້ານຂອງ wafer ຊິລິໂຄນ.

ການຄວບຄຸມຄວາມຖືກຕ້ອງຂອງລະບົບການສະແກນ: ລະບົບການສະແກນໃນທິດທາງສາມມິຕິ X-Y-Z ຂອງຊິລິໂຄນ wafer ຈໍາເປັນຕ້ອງມີຄວາມຖືກຕ້ອງຂອງການຄວບຄຸມສູງທີ່ສຸດເພື່ອຮັບປະກັນວ່າທຸກໆຈຸດທີ່ຢູ່ເທິງຫນ້າຂອງ silicon wafer ສາມາດດໍາເນີນການໄດ້ຢ່າງຖືກຕ້ອງ.

ການຄົ້ນຄວ້າເຕັກໂນໂລຢີການປຸງແຕ່ງ: ການຄົ້ນຄວ້າໃນຄວາມເລິກແລະການເພີ່ມປະສິດທິພາບຂອງເຕັກໂນໂລຢີການປຸງແຕ່ງຂອງເຕັກໂນໂລຢີ D.C.P plasma ແມ່ນຕ້ອງການເພື່ອຊອກຫາຕົວກໍານົດການແລະເງື່ອນໄຂການປຸງແຕ່ງທີ່ດີທີ່ສຸດ.

ການຄວບຄຸມຄວາມເສຍຫາຍຂອງພື້ນຜິວ: ໃນລະຫວ່າງຂະບວນການປຸງແຕ່ງ D.C.P, ຄວາມເສຍຫາຍຂອງແຜ່ນ silicon wafer ຕ້ອງໄດ້ຮັບການຄວບຄຸມຢ່າງເຂັ້ມງວດເພື່ອຫຼີກເວັ້ນຜົນກະທົບທາງລົບຕໍ່ການກະກຽມຕໍ່ໄປຂອງວົງຈອນຊິບ IC.

ເຖິງແມ່ນວ່າເທກໂນໂລຍີ plasma D.C.P ມີຄວາມໄດ້ປຽບຫຼາຍ, ເນື່ອງຈາກວ່າມັນເປັນເຕັກໂນໂລຢີການປຸງແຕ່ງໃຫມ່, ມັນຍັງຢູ່ໃນຂັ້ນຕອນການຄົ້ນຄວ້າແລະການພັດທະນາ. ດັ່ງນັ້ນ, ມັນຈໍາເປັນຕ້ອງໄດ້ຮັບການປິ່ນປົວຢ່າງລະມັດລະວັງໃນການປະຕິບັດຕົວຈິງແລະການປັບປຸງດ້ານວິຊາການແລະການເພີ່ມປະສິດທິພາບຍັງສືບຕໍ່.

![]()

ໂດຍທົ່ວໄປ, ການຂັດສຸດທ້າຍແມ່ນສ່ວນຫນຶ່ງທີ່ສໍາຄັນຂອງຊິລິຄອນ waferຂະບວນການປຸງແຕ່ງ, ແລະມັນແມ່ນກ່ຽວຂ້ອງໂດຍກົງກັບຄຸນນະພາບແລະການປະຕິບັດຂອງວົງຈອນຊິບ IC. ມີການພັດທະນາຢ່າງຕໍ່ເນື່ອງຂອງອຸດສາຫະກໍາ semiconductor, ຄວາມຕ້ອງການດ້ານຄຸນນະພາບຂອງwafers ຊິລິໂຄນຈະສູງຂຶ້ນແລະສູງຂຶ້ນ. ສະນັ້ນ, ການຂຸດຄົ້ນ ແລະ ພັດທະນາເຕັກໂນໂລຊີຂັດໃໝ່ຢ່າງຕໍ່ເນື່ອງຈະເປັນທິດທາງການຄົ້ນຄວ້າທີ່ສຳຄັນໃນຂົງເຂດການປຸງແຕ່ງ wafer ຊິລິຄອນໃນອະນາຄົດ.

ຂໍ້ສະເໜີ Semicorexwafers ຄຸນະພາບສູງ. ຖ້າທ່ານມີຄໍາຖາມໃດໆຫຼືຕ້ອງການລາຍລະອຽດເພີ່ມເຕີມ, ກະລຸນາຢ່າລັງເລທີ່ຈະຕິດຕໍ່ກັບພວກເຮົາ.

ເບີໂທຕິດຕໍ່ #+86-13567891907

ອີເມວ: sales@semicorex.com