- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

ຂະບວນການ CMP ແມ່ນຫຍັງ

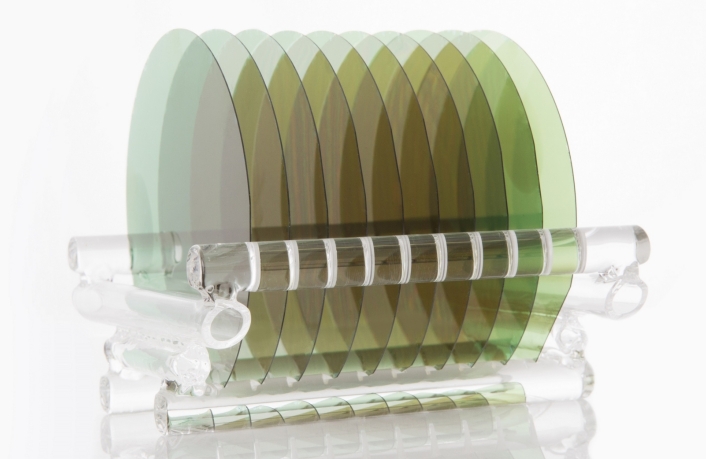

ໃນການຜະລິດ semiconductor, ຄວາມຮາບພຽງໃນລະດັບປະລໍາມະນູແມ່ນຖືກນໍາໃຊ້ເພື່ອອະທິບາຍຄວາມຮາບພຽງຢູ່ທົ່ວໂລກwafer, ດ້ວຍຫົວໜ່ວຍຂອງ nanometers (nm). ຖ້າຫາກວ່າຄວາມຕ້ອງການຮາບພຽງໃນທົ່ວໂລກແມ່ນ 10 nanometers (nm), ນີ້ແມ່ນທຽບເທົ່າກັບຄວາມແຕກຕ່າງລະດັບຄວາມສູງສູງສຸດ 10 nanometers ໃນເນື້ອທີ່ 1 ຕາແມັດ (10nm ໂລກຮາບພຽງແມ່ນເທົ່າກັບຄວາມແຕກຕ່າງລະຫວ່າງຄວາມສູງລະຫວ່າງສອງຈຸດໃດຫນຶ່ງໃນ Tiananmen Square ກັບ. ພື້ນທີ່ຂອງ 440,000 ຕາແມັດບໍ່ເກີນ 30 microns.) ແລະຄວາມຫຍາບຂອງຫນ້າດິນຂອງມັນແມ່ນຫນ້ອຍກວ່າ 0.5um (ເມື່ອປຽບທຽບກັບຜົມທີ່ມີເສັ້ນຜ່າກາງ 75 microns, ມັນເທົ່າກັບຫນຶ່ງ 150,000th ຂອງຜົມ). ຄວາມບໍ່ສອດຄ່ອງໃດໆອາດຈະເຮັດໃຫ້ເກີດວົງຈອນສັ້ນ, ວົງຈອນປິດຫຼືຜົນກະທົບຕໍ່ຄວາມຫນ້າເຊື່ອຖືຂອງອຸປະກອນ. ຄວາມຕ້ອງການຄວາມຮາບພຽງທີ່ມີຄວາມແມ່ນຍໍາສູງນີ້ຕ້ອງໄດ້ຮັບການບັນລຸໂດຍຜ່ານຂະບວນການເຊັ່ນ CMP.

ຫຼັກການຂະບວນການ CMP

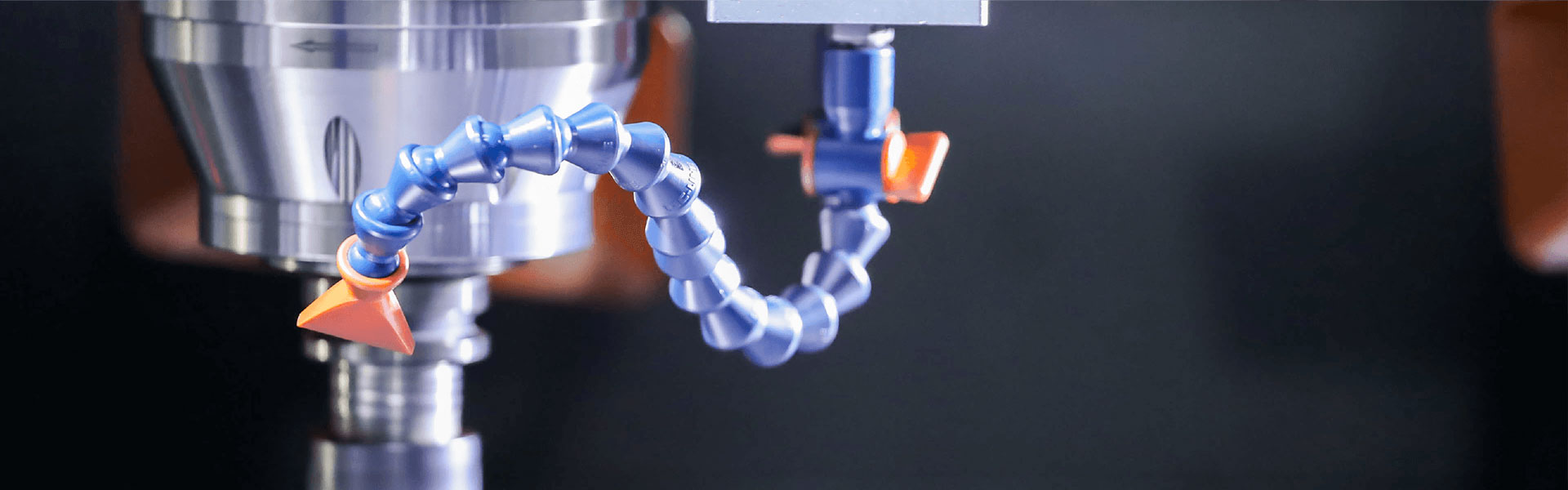

ການຂັດດ້ວຍກົນຈັກເຄມີ (CMP) ແມ່ນເທັກໂນໂລຍີທີ່ໃຊ້ເພື່ອປັບພື້ນຜິວ wafer ໃນລະຫວ່າງການຜະລິດຊິບ semiconductor. ໂດຍຜ່ານປະຕິກິລິຍາເຄມີລະຫວ່າງຂອງແຫຼວຂັດແລະຫນ້າດິນ wafer, ຊັ້ນ oxide ທີ່ງ່າຍຕໍ່ການຈັດການແມ່ນຖືກສ້າງຂຶ້ນ. ຫຼັງຈາກນັ້ນ, ຊັ້ນ oxide ໄດ້ຖືກໂຍກຍ້າຍອອກໂດຍຜ່ານການ grinding ກົນຈັກ. ຫຼັງຈາກການປະຕິບັດທາງເຄມີແລະກົນຈັກຫຼາຍອັນຖືກປະຕິບັດສະລັບກັນ, ພື້ນຜິວ wafer ເປັນເອກະພາບແລະຮາບພຽງຖືກສ້າງຕັ້ງຂຶ້ນ. ສານເຄມີ reactants ອອກຈາກຫນ້າດິນ wafer ແມ່ນລະລາຍໃນຂອງແຫຼວໄຫຼແລະເອົາໄປ, ດັ່ງນັ້ນຂະບວນການຂັດ CMP ປະກອບມີສອງຂະບວນການ: ເຄມີແລະທາງດ້ານຮ່າງກາຍ.