- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

SiGe ແລະ Si Selective Etching Technology

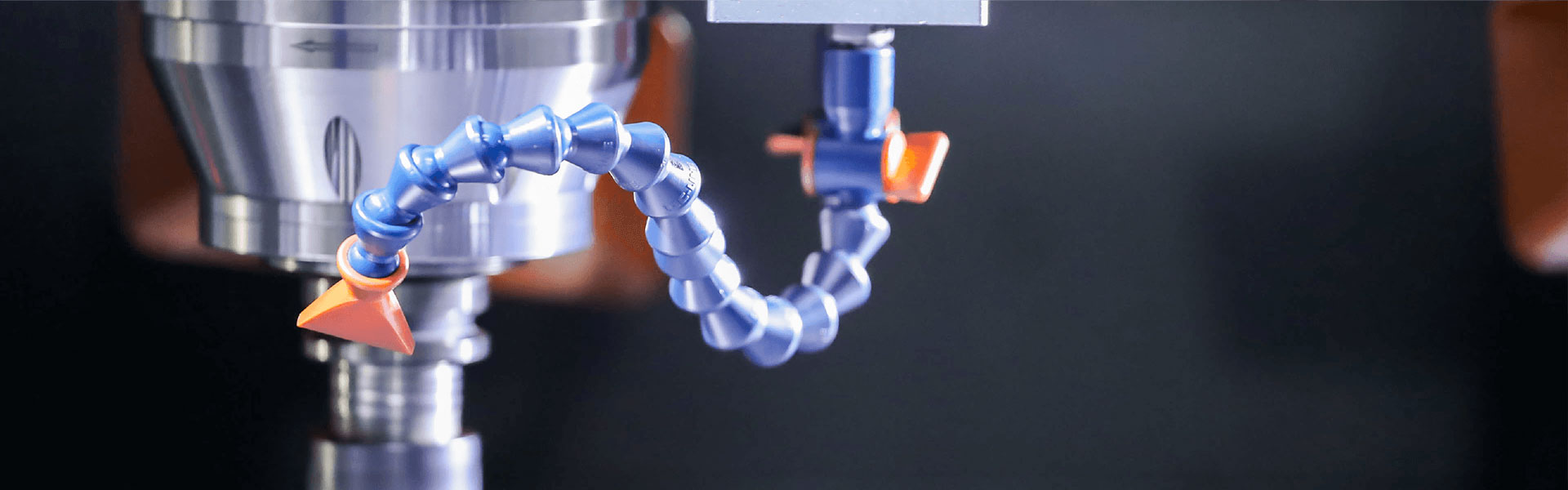

Gate-All-Around FET (GAAFET), ໃນຖານະທີ່ເປັນສະຖາປັດຕະຍະກໍາຂອງ transistor ລຸ້ນຕໍ່ໄປທີ່ກຽມພ້ອມທີ່ຈະທົດແທນ FinFET, ໄດ້ເອົາໃຈໃສ່ຢ່າງຫຼວງຫຼາຍສໍາລັບຄວາມສາມາດໃນການສະຫນອງການຄວບຄຸມໄຟຟ້າສະຖິດທີ່ເຫນືອກວ່າແລະເພີ່ມປະສິດທິພາບໃນຂະຫນາດຂະຫນາດນ້ອຍກວ່າ. ຂັ້ນຕອນທີ່ສໍາຄັນໃນການຜະລິດ GAAFETs n-type ກ່ຽວຂ້ອງກັບການເລືອກສູງຮອຍຂີດຂ່ວນຂອງ SiGe:Si stacks ກ່ອນທີ່ຈະຝາກຂອງ spacers ພາຍໃນ, ການຜະລິດ nanosheets ຊິລິໂຄນແລະຊ່ອງການປ່ອຍ.

ບົດຄວາມນີ້ delves ເຂົ້າໄປໃນການຄັດເລືອກເຕັກໂນໂລຊີ ຮອຍຂີດຂ່ວນມີສ່ວນຮ່ວມໃນຂະບວນການນີ້ແລະແນະນໍາສອງວິທີການ etching ໃຫມ່ - etching ທີ່ບໍ່ມີອາຍແກັສ plasma oxidative ສູງແລະການ etching ຊັ້ນປະລໍາມະນູ (ALE) - ເຊິ່ງສະເຫນີວິທີແກ້ໄຂໃຫມ່ສໍາລັບການບັນລຸຄວາມແມ່ນຍໍາສູງແລະການຄັດເລືອກໃນການ etching SiGe.

SiGe Superlattice Layers ໃນໂຄງສ້າງ GAA

ໃນການອອກແບບຂອງ GAAFETs, ເພື່ອເພີ່ມປະສິດທິພາບຂອງອຸປະກອນ, ຊັ້ນສະລັບຂອງ Si ແລະ SiGe ແມ່ນປູກ epitaxially ໃນ substrate ຊິລິຄອນ, ປະກອບເປັນໂຄງສ້າງ multilayer ທີ່ຮູ້ຈັກເປັນ superlattice. ຊັ້ນ SiGe ເຫຼົ່ານີ້ບໍ່ພຽງແຕ່ປັບຄວາມເຂັ້ມຂົ້ນຂອງຜູ້ໃຫ້ບໍລິການ, ແຕ່ຍັງປັບປຸງການເຄື່ອນໄຫວຂອງເອເລັກໂຕຣນິກໂດຍການແນະນໍາຄວາມກົດດັນ. ຢ່າງໃດກໍຕາມ, ໃນຂັ້ນຕອນຂະບວນການຕໍ່ໄປ, ຊັ້ນ SiGe ເຫຼົ່ານີ້ຈໍາເປັນຕ້ອງໄດ້ໂຍກຍ້າຍອອກຢ່າງແນ່ນອນໃນຂະນະທີ່ຮັກສາຊັ້ນຊິລິໂຄນ, ຮຽກຮ້ອງໃຫ້ມີເຕັກໂນໂລຢີ etching ທີ່ມີການຄັດເລືອກສູງ.

ວິທີການສໍາລັບການເລືອກ Etching ຂອງ SiGe

ການຝັງຕົວທີ່ບໍ່ມີອາຍແກັສອອກຊິເຈນສູງໃນ plasma

ການຄັດເລືອກຂອງອາຍແກັສ ClF3: ວິທີການ etching ນີ້ໃຊ້ອາຍແກັສອອກຊິເຈນສູງທີ່ມີການຄັດເລືອກຫຼາຍ, ເຊັ່ນ ClF3, ບັນລຸອັດຕາສ່ວນການຄັດເລືອກ SiGe: Si ຂອງ 1000-5000. ມັນສາມາດໄດ້ຮັບການສໍາເລັດຢູ່ໃນອຸນຫະພູມຫ້ອງໂດຍບໍ່ມີການເຮັດໃຫ້ເກີດຄວາມເສຍຫາຍ plasma.

ປະສິດທິພາບອຸນຫະພູມຕ່ໍາ: ອຸນຫະພູມທີ່ດີທີ່ສຸດແມ່ນປະມານ 30 ° C, ຮັບຮູ້ເຖິງການເລືອກສູງ etching ພາຍໃຕ້ເງື່ອນໄຂອຸນຫະພູມຕ່ໍາ, ຫຼີກເວັ້ນການເພີ່ມຂຶ້ນງົບປະມານຄວາມຮ້ອນເພີ່ມເຕີມ, ເຊິ່ງເປັນສິ່ງສໍາຄັນສໍາລັບການຮັກສາປະສິດທິພາບອຸປະກອນ.

ສະພາບແວດລ້ອມແຫ້ງ: ທັງຫມົດຂະບວນການ ຮອຍຂີດຂ່ວນແມ່ນດໍາເນີນພາຍໃຕ້ສະພາບແຫ້ງແລ້ງຢ່າງສົມບູນ, ກໍາຈັດຄວາມສ່ຽງຕໍ່ການຍຶດຫມັ້ນຂອງໂຄງສ້າງ.

ການອັດຊັ້ນປະລໍາມະນູ (ALE)

ລັກສະນະການຈໍາກັດຕົນເອງ: ALE ແມ່ນວົງຈອນສອງຂັ້ນຕອນເຕັກໂນໂລຊີ etching, ບ່ອນທີ່ຫນ້າດິນຂອງວັດສະດຸທີ່ຈະ etched ໄດ້ຖືກດັດແກ້ທໍາອິດ, ແລະຫຼັງຈາກນັ້ນຊັ້ນດັດແກ້ໄດ້ຖືກໂຍກຍ້າຍອອກໂດຍບໍ່ມີຜົນກະທົບຕໍ່ພາກສ່ວນທີ່ບໍ່ໄດ້ຮັບການແກ້ໄຂ. ແຕ່ລະຂັ້ນຕອນແມ່ນຈໍາກັດຕົນເອງ, ຮັບປະກັນຄວາມແມ່ນຍໍາໃນລະດັບຂອງການຖອນພຽງແຕ່ສອງສາມຊັ້ນປະລໍາມະນູໃນເວລາ.

Cyclic etching: ສອງຂັ້ນຕອນທີ່ໄດ້ກ່າວມາຂ້າງເທິງແມ່ນຮອບວຽນຊ້ໍາຊ້ອນຈົນກ່ວາຄວາມເລິກ etching ທີ່ຕ້ອງການແມ່ນບັນລຸໄດ້. ຂະບວນການນີ້ເຮັດໃຫ້ ALE ບັນລຸໄດ້ຄວາມແມ່ນຍໍາລະດັບປະລໍາມະນູຢູ່ຕາມໂກນຂະຫນາດນ້ອຍຢູ່ຝາພາຍໃນ.

ພວກເຮົາຢູ່ Semicorex ຊ່ຽວຊານໃນSiC/TaC coated graphite solutionsນໍາໃຊ້ໃນຂະບວນການ Etching ໃນການຜະລິດ semiconductor, ຖ້າທ່ານມີຄໍາຖາມຫຼືຕ້ອງການລາຍລະອຽດເພີ່ມເຕີມ, ກະລຸນາຢ່າລັງເລທີ່ຈະຕິດຕໍ່ກັບພວກເຮົາ.

ເບີໂທຕິດຕໍ່: +86-13567891907

ອີເມວ: sales@semicorex.com